Tampilan:1 创始人: Site Editor Publish Time: 2026-02-14 Origin: Site

Chip bonding process: a panoramic analysis

from basic processes to technological innovations

1. Key hubs in the packaging process: the

positioning and value of chip bonding

As a bridge between chips and application

terminals, semiconductor packaging is like the gear set of a precision clock,

and every link needs to be tightly seamed. After the dicing process divides the

wafer into individual chips, the chip bonding process takes over the

"baton" and takes on the key mission of accurately placing these tiny

chips (the smallest size is only 0.3mm×0.3mm) on the packaging substrate.

Whether it's traditional lead frames, general-purpose printed circuit boards

(PCBs), or advanced ceramic substrates, the bonding process requires a secure

connection to the chip.

The essence of bonding technology is to

establish a trinity system of "physical fixation-electrical

connection-thermal management": physical fixation requires a bonding

strength of 10-50g (varies depending on the chip size), can withstand the mechanical

shock of the post-packaging process (such as injection molding pressure during

molding), and the electrical connection needs to ensure a contact resistance of

< 50mΩ, and maintain stability in the temperature cycle of

-55°C~125°CThermal management requires a thermal conductivity of > 1W/m・K of the bonding layer to ensure that

the heat generated during the operation of the chip is effectively transferred

to the substrate

With the development of advanced processes

such as FinFET and GAA, the power density of chips has exceeded 300W/cm², and

the heat dissipation performance of the bonding process has become a key

bottleneck restricting the release of chip performance. One test data shows

that for every 0.1°C/W reduction in thermal resistance of the bonding layer,

the chip can increase the overclocking headroom by 5-8%, highlighting the

strategic position of bonding technology in modern semiconductor manufacturing.

2. The genealogy and evolution of bonding

technology: a leap from tradition to modernity

Semiconductor bonding technology has been

developed for more than 70 years, forming a clear technical context, each

optimized for specific application scenarios:

2.1 Traditional bonding technology system

Traditional bonding technology is

characterized by "step-by-step connection", where the chip is fixed

before the electrical interconnection is realized: Die Bonding:

Also known as chip placement, the core is

to fix the chip to the substrate through adhesives. According to the type of

adhesive, it can be divided into organic adhesive bonding: using polymer

materials such as epoxy resin and polyimide, suitable for medium and low power

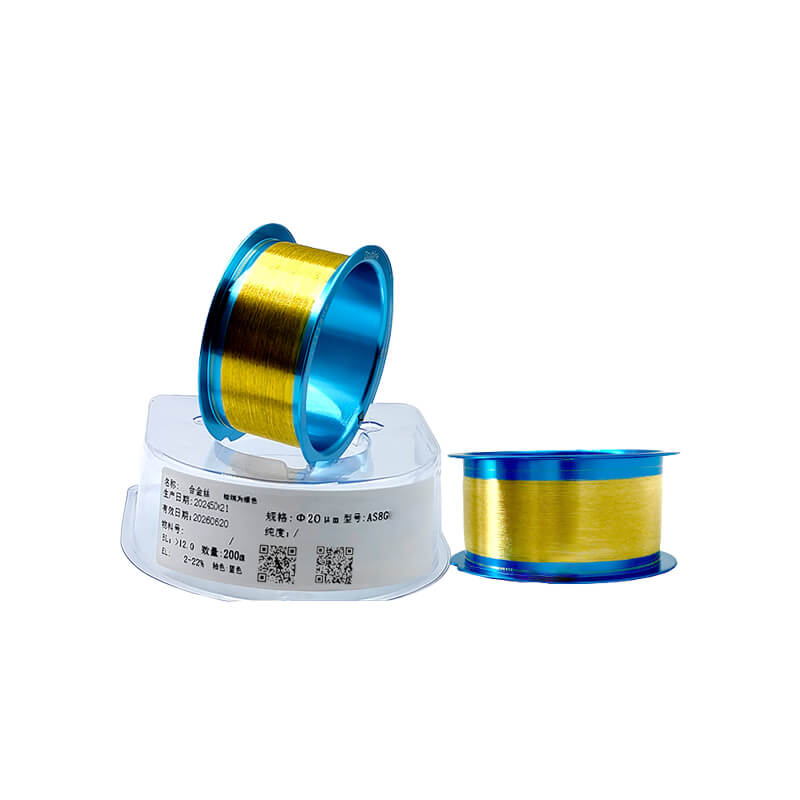

chips (<10W), and eutectic bonding: using eutectic reactions of gold-tin

(AuSn), copper-tin (CuSn) and other alloys (such as Au80Sn20 eutectic point

280°C), thermal conductivity can reach 50W/m·K or

more, suitable for high-power devices

Wire bonding: After the chip is fixed, the

chip pad is connected to the substrate pins through a bonded alloy wire

(diameter 15-50μm). According to the bonding method, it is divided into

spherical bonding (mainly gold wire) and wedge bonding (mainly aluminum wire),

which is still the mainstream solution for low-end packaging (about 65% of the

market).

2.2 Breakthroughs in modern bonding

technology

Modern technology, represented by flip

chips, has achieved a "one-step" connection revolution:

Flip Chip Bonding: Invented by IBM in the

late 1960s, it is directly connected to the substrate by prefabricating bumps

on the chip pads, flipping them over. This technology increases bond point

density to more than 10 times that of traditional wire bonding, and is now 80%

penetrated in high-end chips such as smartphone APs and GPUs.

Its technical features include:

Bump material: From traditional solder

(SnPb, SnAgCu) to copper pillar bump (Cu Pillar), the diameter is reduced from

200μm to 15μm, and the connection method: no wires are required, and the

intermetallic compound (IMC) is formed by reflow soldering to achieve ohmic

contact

Reliability: Underfill materials are

required to alleviate thermal mismatch stress, so that the temperature cycle

life can reach more than 1000 times

The driving force behind technological

evolution has always revolved around three core metrics: bond density (number

of bond points per unit area), signal transmission speed, and manufacturing

cost. From 10 bond points per square millimeter in the 1980s to more than

10,000 today achieved with hybrid bonding technology, density has increased by

three orders of magnitude, supporting the continued growth of chip integration.

3. The complete process chain of chip

bonding: precision control from preparation to completion

The chip bonding process is like a

"surgical operation" in the microscopic world, requiring precise

cooperation through multiple processes:

3.1 Preliminary preparation: precise

deployment of materials and equipment

Adhesive coating process:

Choose the appropriate coating method based

on chip size and power: Key parameters: The viscosity of epoxy adhesives is

usually controlled at 1000-5000cP (25°C) to ensure stable shape after coating.

Dispensing: Suitable for large-size chips (>5mm²), the diameter of the dot

is controlled at 1/3-1/2 of the chip size, the accuracy is ±50μm, and the

printing (Stencil Printing): suitable for mass production of small-size chips,

with a uniformity of adhesive thickness of up to ±10μm Thin film (DAF):

pre-affixed on the back of the wafer, directly bonded after scribing, with a

thickness control accuracy of ±2μm

Substrate pretreatment: The substrate

surface needs to be cleaned (to remove oxidation and contaminants) and activate

(to increase surface energy):

Cleaning method: plasma cleaning (Ar/O₂ gas mixture) or

ultrasonic cleaning (megasonic frequency 1MHz), activation

standard: contact angle < 30° to ensure good wetting of the adhesive.

3.2 Core Operation: Micron-level control of

pick-and-place

Pick & Place is the core of the bonding

process, testing the positioning accuracy and operational stability of the

equipment:

Separating chips from dicing tape faces two

major challenges: The solution uses "push-up + suction" composite

technology: chip sticking: adjacent chips are only 50-100μm apart, which is

prone to adhesion, and mechanical damage: when the chip thickness is <

100μm, direct suction can easily lead to chipping (strength <

10MPa).Ejector: Apply a force of 0.1-1N through the thimble to raise the edge

of the chip by 5-10μm, and Collet: Use a vacuum nozzle (0.3-2mm diameter), and

the suction force is controlled at 5-50mN to avoid chip deformation

Place process: Accurately position the chip

to the target position of the substrate, key indicators include: Positioning

accuracy: ±1μm (high-end equipment), ensure bond point alignment deviation <

25% pad size, placement pressure: 5-50cN, dynamically adjust according to chip

thickness (thin chip < 20cN), placement speed: 0.5-2 seconds/piece,

Balancing efficiency and precision, statistics from an advanced packaging

factory show that for every 1 μm improvement in placement accuracy, bond yield

can increase by 3-5%, highlighting the decisive impact of equipment accuracy on

process quality.

3.3 Curing and Joining: Precise control of

temperature field

The curing/reflow process after bonding is

key to forming a stable connection:

Typical temperature profile quality

determination: > 95% cure (DSC), shear strength > 15MPa. Preheating

Section: 80-120°C/30-60 seconds (solvent removal), Curing Section:

150-200°C/60-120 seconds (Crosslinking Reaction), Cooling Section: Natural

cooling to < 50°C (avoiding thermal shock).Typical curves for lead-free

solder (e.g., SAC305) for connection of flip chip bumps: Key quality

indicators: IMC layer thickness 1-3μm, void rate < 10% (X-ray inspection).

Preheat: 150-180°C/60-90 sec, Reflow: 240-260°C/30-60 sec (to ensure complete solder

melting) Cooling: Rate < 4°C/s (to inhibit abnormal IMC growth).

4. Material technology innovation: the

material basis of bonding quality

The performance of bonding materials

directly determines the connection reliability, and in recent years, it has

shown a diversified development trend:

4.1 Optimization of traditional adhesives

Performance is enhanced by adding

functional fillers: Operating characteristics: Pot Life > 8 hours to meet

mass production needs.

Thermally conductive fillers: alumina (Al₂O₃), boron nitride (BN), etc., the filling amount of 50-70% can

increase the thermal conductivity from 0.2W/m·K to

1-5W/m・K, and the conductive filler: silver powder

(Ag), copper powder (Cu), and the volume resistivity can reach 10⁻⁴ Ω・cm or less, toughener: rubber particles or nanofibers to improve

impact resistance (elongation at break increased from 5% to 15%)

4.2 The rise of chip-bonded films (DAFs).

DAF technology solves the thickness control

challenge of liquid adhesives with preformed films:

It typically has a three-layer structure: substrate layer: polyimide or epoxy resin (5-20μm thickness), bonding layer: modified epoxy resin (10-50μm thickness), release layer: silicone oil-treated PET film (peeled off when used). Thickness accuracy: ±2μm, much higher than the ±20μm of liquid dispensing, simplified process: eliminating dispensing and partial curing steps, increasing production efficiency by 30%, multi-chip support: suitable for stacked die for reliable connection between chipsAir residue: bubbles may form (diameter > 50μm is considered a defect), the vacuum level of the lamination equipment is required to be < 10Pa, equipment investment: special laminator and hot pressing equipment are required, the initial investment is increased by about 20%, and the application rate of DAF in multi-chip packaging (MCP) has reached 45%, especially in the field of memory packaging (such as DDR4/ DDR5) has become the mainstream solution.

4.3 Emerging material systems

Nano solder: Tin-based solder with a

particle size of < 100nm with a melting point reduced by 30-50°C compared to

traditional solder, suitable for thermal device bonding.

Metal matrix composites: such as

silver-graphene composites, the thermal conductivity can reach more than 400W/m·K, which is close to the level of pure silver, and the cost is

reduced by 30%.

The direction of material innovation is to

find the best balance between "thermal conductivity - electrical

conductivity - cost - processability", and the current industry research

hotspots are focused on lead-free, low-temperature and high thermal

conductivity.

5. Process challenges and solutions:

practical paths to improve yield

During the chip bonding process, various

factors can lead to defects that need to be addressed in a targeted manner:

5.1 Analysis of common process defects

|

Defect type |

Causes |

Incidence |

Degree of harm |

|

Chip warping |

Uneven adhesive thickness (variable >

10μm) |

8-12% |

High (causing difficulty in subsequent

wire bonding) |

|

empty |

No air bubbles are expelled from the

adhesive |

5-8% |

Medium (affects heat dissipation and

strength) |

|

offset |

Placement positioning error > 5 μm |

3-5% |

High (may cause a short circuit) |

|

Adhesive spillage |

Too much application or too much pressure |

6-9% |

Medium (contaminated pads) |

5.2 Key process optimization measures

Using a "gradient cure" process:

initial curing at 120°C (30 minutes) to release some of the stress, then

heating up to 180°C for full curing, which reduces the amount of warpage from

50μm to less than 15μm. Combined with vacuum assistance: Applied at the initial

curing stage - 0.09MPa vacuum for 10 minutes can reduce the voiding rate from

8% to less than 1%. Combined alignment with "vision + laser": on the

basis of visual positioning (±3μm), laser ranging corrects the Z-axis height (±1μm)

to ensure uniform placement pressure. Establish a mathematical model of

"chip size - adhesive dosage": for a square chip with a side length

L, the dispensing amount V=k×L² (k is the coefficient, usually

0.0015-0.002mm³/mm²).

One case shows that through the

comprehensive implementation of the above measures, the bonding yield rate of a

packaging plant has increased from 82% to 97.5%, saving more than 3 million

yuan per year.

6. Technology development trend: the future

of ultra-thin and integration

As the semiconductor industry moves towards

the More than Moore era, bonding technology is moving in three directions:

Ultra-thin chip bonding:

For ultra-thin chips below 50μm, develop

flexible nozzles (with silicone or polyimide materials) and low-stress

adhesives (modulus of elasticity <1GPa) to avoid chip fragmentation. Stable

bonding of 20μm thick chips has been achieved with a yield of > 95%.

Heterogeneous Integrated Bonding:

It supports hybrid bonding of chips of

different materials and processes, such as the bonding of Si chips with

compound semiconductors such as GaN and SiC, with a temperature control

accuracy of up to ±1°C to ensure that the stress caused by the difference in

thermal expansion between the two materials is minimized.

Intelligent Process:

Introducing machine vision and AI

algorithms to detect adhesive coating quality in real-time (> 99% accuracy),

predict bond strength (error < 5%), and adaptively adjust process parameters

(response time < 100ms).

The development of these technologies will

promote the transformation of bonding processes from

"experience-driven" to "data-driven", providing core

support for advanced packaging forms such as chiplets and 3D ICs.

epilogue

The chip bonding process may seem like a

simple "paste" action, but it is actually a combination of materials

science, precision mechanics, thermals and control engineering. From

millimeter-level to micron-level to nanometer-level precision leap, from single

chip to multi-chip integration, bonding technology has always been the key

fulcrum of semiconductor packaging innovation.

In the future, as the demand for chip

performance continues to improve, bonding technology will face higher

challenges: it must not only achieve ultra-fine bonding below 1μm, but also

meet the high-temperature reliability above 1000°C; It is necessary to reduce

manufacturing costs and increase integration density. This requires

collaborative innovation in the upstream and downstream of the industrial chain

to form a complete technical ecology from materials, equipment to processes.

For industry practitioners, grasping the

development trend of bonding technology can not only enhance product

competitiveness, but also occupy a favorable position in the new round of

transformation of the semiconductor industry. Just as packaging technology has

changed from a "supporting role" to a "protagonist", the

bonding process is also jumping from a "back-end process" to a

"core technology", writing a new chapter in semiconductor

manufacturing.

Su Gongwang Security 32058302004438

Su Gongwang Security 32058302004438