Tampilan:1 创始人: Site Editor Publish Time: 2026-04-07 Origin: Site

Full analysis of traditional chip

packaging process: precision transformation from wafer to finished product

In the long chain of the semiconductor

industry, the packaging process is like the "final molding workshop"

of chips, transforming the processed wafers into electronic components that can

be directly applied. This process may seem like a simple "packaging",

but in fact it includes more than 15 precise processes, each of which needs to

be controlled to the micron level - the equivalent of engraving on a

cross-section of a hair. Although the traditional packaging process has been

developed for more than half a century, its core logic has always revolved

around three major goals: protecting the chip from environmental damage,

achieving efficient output of electrical performance, and meeting the size and

cost requirements of downstream applications. This article will systematically

disassemble the complete process of traditional packaging, revealing the

technical details and quality control mysteries behind each process.

1. Wafer thinning: precision grinding

for chip "slimming"

Wafer thinning is the first critical process in traditional packaging, as it "paves the way" for subsequent processes. The thickness of the original wafer (8" or 12") is typically 600-800μm, which not only increases the package size, but also leads to inefficient heat dissipation and signal transmission delays. The thinning process uses mechanochemical grinding (CMP) technology to precisely control wafer thickness from 50-150 μm, and in some special applications it can even be reduced to less than 20 μm – the thickness of two A4 sheets.

The triple technical objectives of the

thinning process are clear. From the perspective of space, the thinned wafer

can reduce the thickness of the final package by more than 40%, meeting the

needs of mobile devices and other devices for thinness and lightness. From a thermal management perspective, the reduction in thickness reduces

the thermal resistance from 25°C/W to less than 10°C/W, and test data from a

power device shows that the operating temperature of a chip thinned to 100μm is

reduced by 15°C compared to the unthinned sample; In terms of electrical

performance, thinner wafers effectively reduce parasitic capacitance (from

0.5pF to 0.2pF) and on-resistance (10-15% reduction), reducing high-frequency

signal transmission delays by 20%.

The technical challenges of precision

grinding cannot be underestimated. When the thickness

is less than 100μm, the flexural strength of the wafer drops from the original

300MPa to less than 100MPa, which is very easy to crack in subsequent

processes. For this reason, modern thinning equipment (e.g. DISCO DGP-8760)

uses a "step-by-step grinding" strategy: 70% of the thickness is

first removed with a coarse abrasive wheel (1200 mesh) with a feed rate of

5μm/s; Then switch to a fine grinding wheel (3000 mesh) to remove 25%, and the

feed rate is reduced to 1μm/s; Finally, the remaining 5% is removed by chemical

etching to avoid the accumulation of mechanical stress. The ionized water

cooling system (flow rate 500mL/min±50) is used throughout the process to ensure

that the grinding temperature does not exceed 40°C to prevent the wafer from

bending due to thermal stress (the bending degree should be controlled at

<50μm).

The quantitative standards of quality

testing are strictly standardized. The thinned wafer

needs to meet the following requirements: thickness uniformity (TTV) < 5 μm

(12-inch wafer), surface roughness Ra< 0.5 nm, and chipping size < 10 μm.

Statistics from one packaging plant show that when the TTV is controlled within

3 μm, the yield of subsequent cutting steps can reach 99%, and when the TTV

exceeds 8 μm, the yield plummets to 85%.

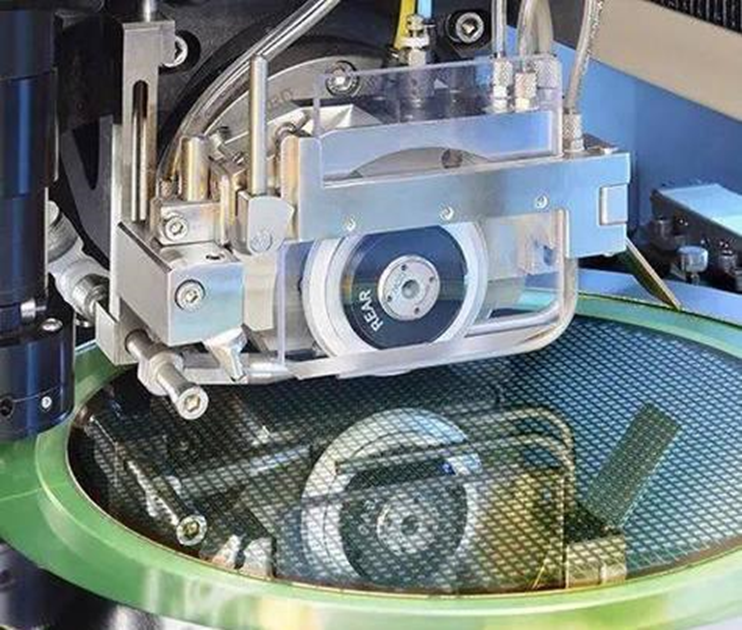

2. Wafer cutting: precise

"cutting" of chip separation

The thinned wafer is like an integrated

circuit map, which needs to be separated into separate dies by dicing. The

accuracy of this process directly determines the integrity of the chip - a

deviation of 0.1mm can lead to the scrapping of chips worth hundreds of yuan.

As chip sizes evolve from millimeters to submillimeters, cutting lane widths

have shrunk from the traditional 100μm to less than 50μm, equivalent to the

diameter of a hair.

Protective measures before cutting are crucial. A blue protective film (UV film) should be applied to the front of the wafer (active area), and its viscosity should be precisely controlled at 50-80g/in (1in=25.4mm) - too low viscosity will cause chip displacement during cutting, and too high will cause damage during subsequent take-up. The lamination process takes place in a Class 100 clean room, ensuring a bubble rate < 0.1% and a bubble diameter < 50 μm. For ultra-thin wafers (<50μm), an additional layer of support glass is applied to prevent wafer deformation during cutting.

The iterative evolution of the three

generations of cutting technology is clearly visible. As a first-generation

technology, mechanical cutting uses diamond blades (20-50μm thickness) that

rotate at high speed (30,000-40,000rpm) to achieve separation by mechanical

force, and has the advantage of low cost (blade life of about 500 wafers), but

it has the defects of large chipping edges (up to 20μm) and slow speed (15

minutes per 8-inch wafer), which has gradually been

phased out.

As a second-generation technology, laser

cutting is divided into two modes: full cutting and hidden cutting. The all-cut

mode burns through the wafer directly with a high-energy CO₂

laser (wavelength 10.6μm) at a cutting speed of up to 100mm/s, which is 5% of

mechanical cutting but can produce heat-affected zones

(HAZ) and debris. The hidden cutting mode is more precise: first, a UV laser

(wavelength 355nm) is used to form a modified layer inside the wafer (20-30μm

from the surface), and then the chip is separated by mechanically stretching

the back tape, and the heat-affected zone can be controlled at <5μm and the

chipping edge is <3μm, which is especially suitable for cutting precision

chips such as 3D NAND.

As a third-generation technology, plasma

cutting achieves separation through the chemical reaction between CF₄/O₂ plasma

and silicon, and the cutting path width can be reduced to 20μm, almost without

damage, but the equipment cost is up to 10 times that of mechanical cutting,

mainly used for advanced process chips below 5nm. Data from one fab shows that

plasma cutting can result in 10% more effective chips per wafer, significantly

reducing the cost per unit.

Key indicators of cut quality include: cutting path deviation <5 μm, chip dimensional accuracy ± 10 μm,

and surface cleanliness (10 < with particle count > 0.3 μm). Automated

optical inspection (AOI) equipment inspects 100% of each chip, ensuring that

there are no defects such as cracks and chipping.

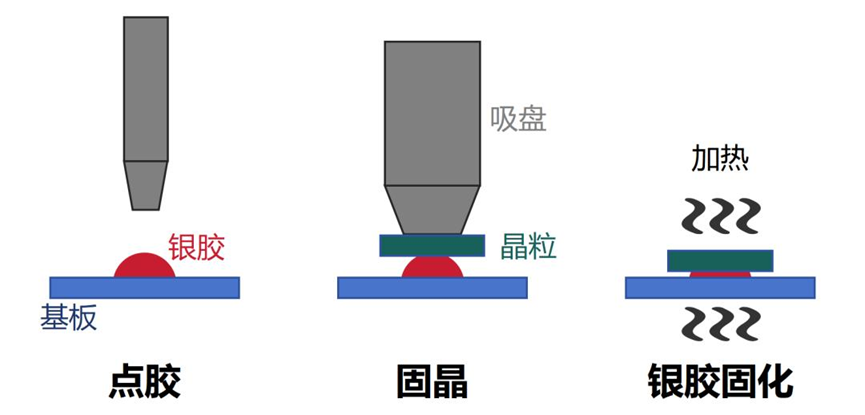

3. Die Attach: The precision of chips

"settles down"

The cut chip needs to be fixed on the packaging substrate through the patch process, which is like "settling down" for the chip. The accuracy and strength of the patch directly affect the subsequent bond quality, and a 0.1mm offset can lead to bond failure. Modern patch technology has achieved positioning accuracy of ±2μm, which is equivalent to 1/25 of the diameter of a hair.

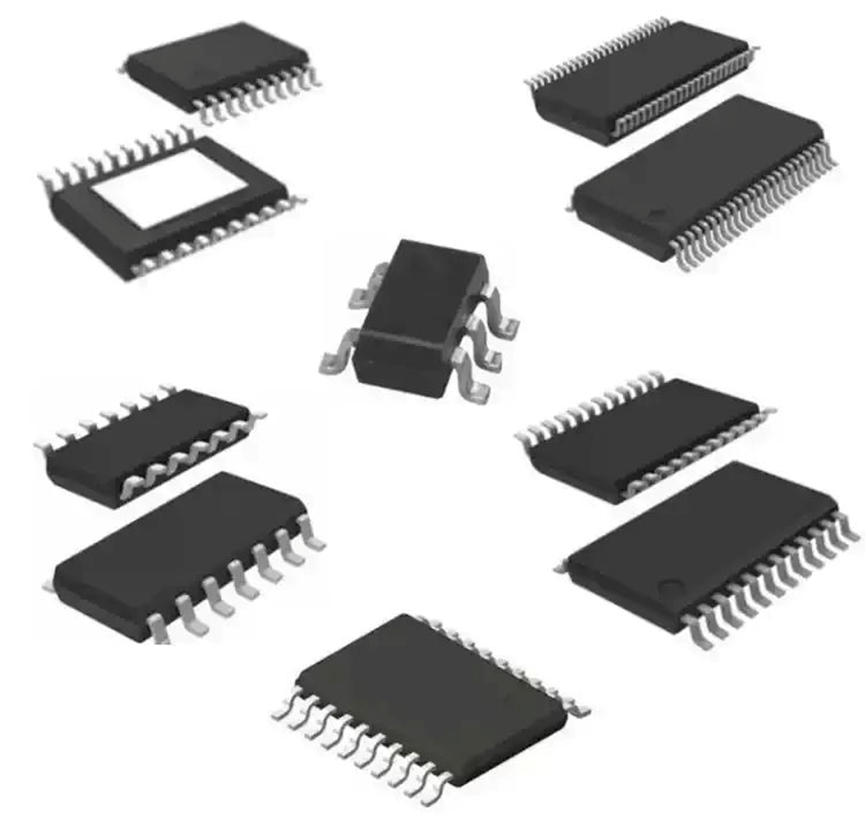

The technical characteristics of

packaging substrates are diverse. There are two types of substrates commonly

used in traditional packaging: lead frames and IC substrates. The lead frame is

made of copper alloy (C19400), with a thickness of 0.2-0.5mm, nickel plated

(3-5μm) on the surface to prevent oxidation, low cost (about 0.1 yuan/ piece), suitable for traditional packaging such as SOP and QFP; IC

carrier boards are high-density PCBs with line widths/spacing of up to

20μm/20μm, using BT resin or ABF materials, which can achieve more I/O pins and

cost 5-10 times more than lead frames, and are used in advanced packaging such

as BGA and CSP.

Each of the three mainstream patch

technologies has its own focus. Epoxy bonding is the most commonly used method,

where silver glue (epoxy + silver powder, 70-85% silver content) is applied to the substrate through a dispenser (accuracy ±5μm),

then the chip is pressed (pressure 50-100g) and baked at 150°C for 60 minutes

to cure. The thermal conductivity of silver adhesive can reach 1-5W/m・K and the bonding strength is > 20MPa, making it suitable for

low- and mid-range products such as consumer electronics.

Eutectic bonding is connected by Au-Si

(melting point 363°C) or Sn-Au (melting point 280°C) eutectic alloy, heated to

eutectic temperature in a nitrogen atmosphere to form an intermetallic

compound, with a thermal conductivity of > 30W/m・K and a bonding strength of > 30MPa, which is suitable for

high-end fields such as aerospace and military industry, but the process is

complex and the cost is 5 times that of silver glue.

Soldering bonding is divided into soft

brazing (Sn-Pb alloy, melting point 183°C) and hard brazing (Au-Ge alloy,

melting point 356°C), which realize the connection through the melting of the

solder, and is suitable for high-current scenarios such as power devices. Under

the trend of lead-free, Sn-Ag-Cu (SAC305) solder is widely used, with a melting

point of 217°C and RoHS compliant.

The technology of SMD equipment has evolved significantly. From manual placement (accuracy ±50μm) to semi-automatic placement (±20μm) to ±2μm in fully automated placement machines such as K&S Maxum, the speed has increased from hundreds to tens of thousands of chips per hour. The placement machine uses a dual vision system (top and bottom cameras) to achieve precise alignment by identifying the mark points on the chip and substrate, and the image processing time < 10ms. According to data from a packaging plant, the yield rate increased from 95% to 99.5% after fully automated placement, reducing waste of 5,000 chips per day.

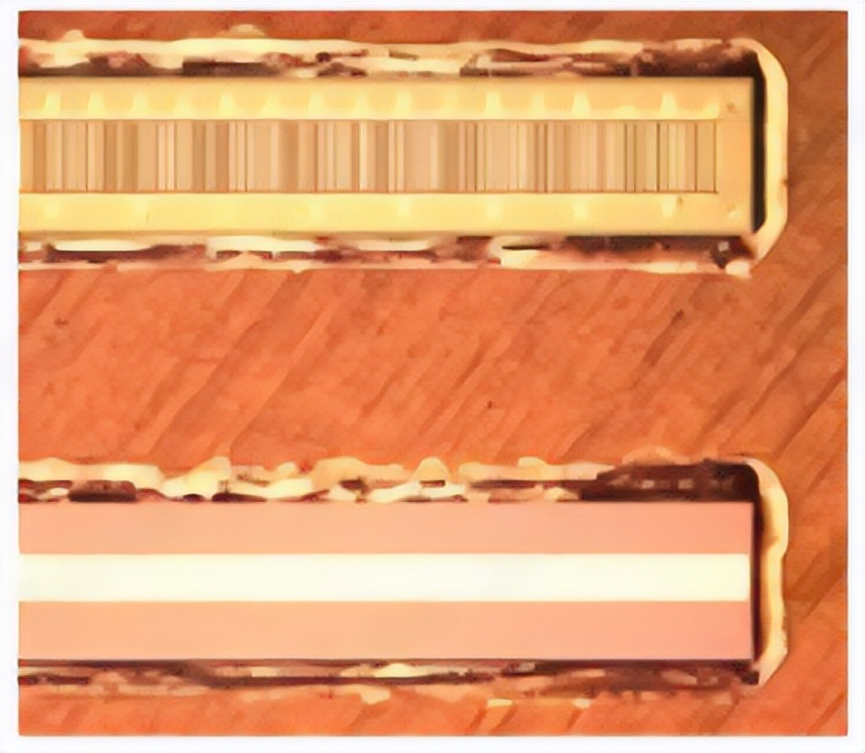

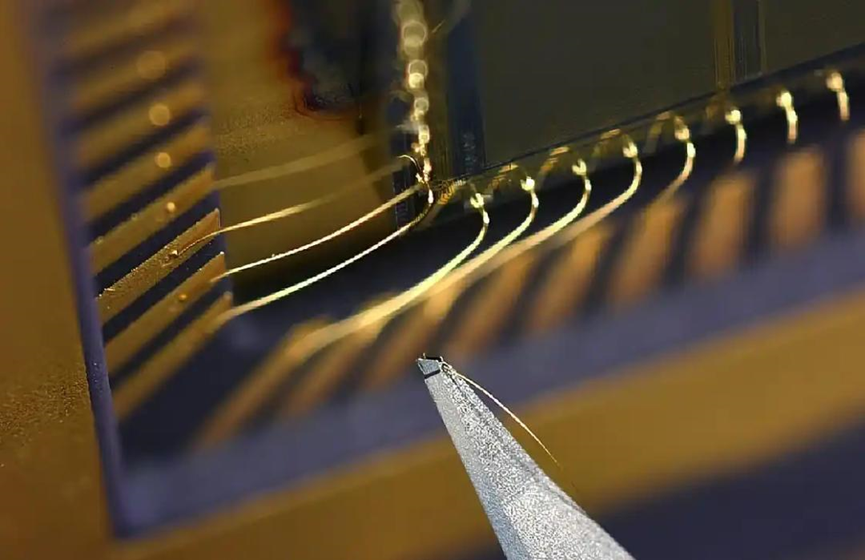

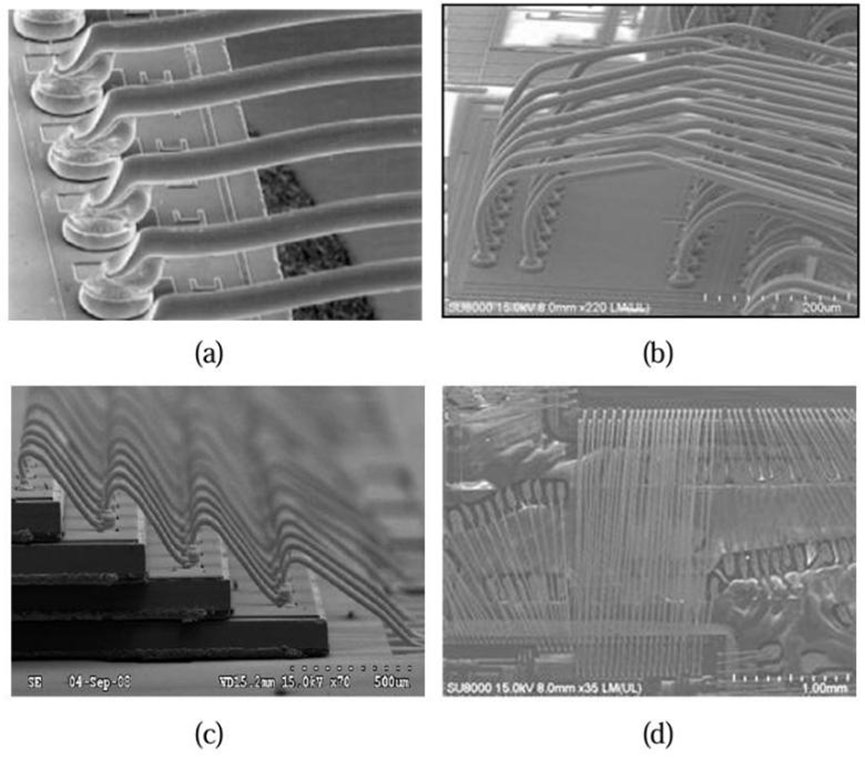

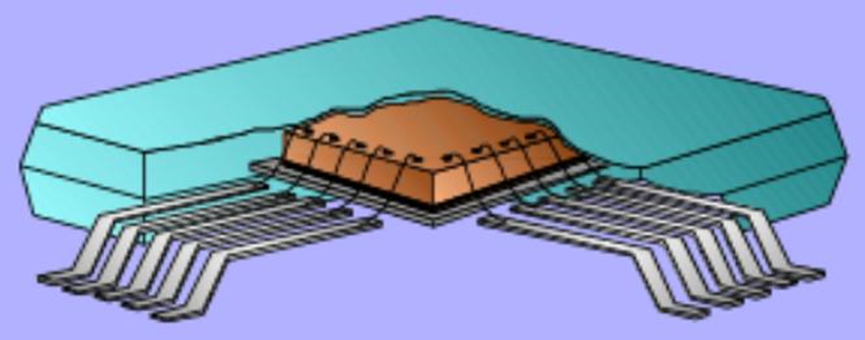

4. Wire Bonding: The Microscopic

"Bridge" of Electrical Connections

After the placement is completed, an electrical connection needs to be established between the chip pad and the substrate through the wire soldering process, which is like "laying wires" for the chip. The number of gold wires that need to be soldered for each chip ranges from a few to thousands, and it is no less difficult to complete the precise connection of gold wires with a diameter of 25-50μm under a microscope than to erect a steel wire with the thickness of a hairline at an altitude of 100 meters.

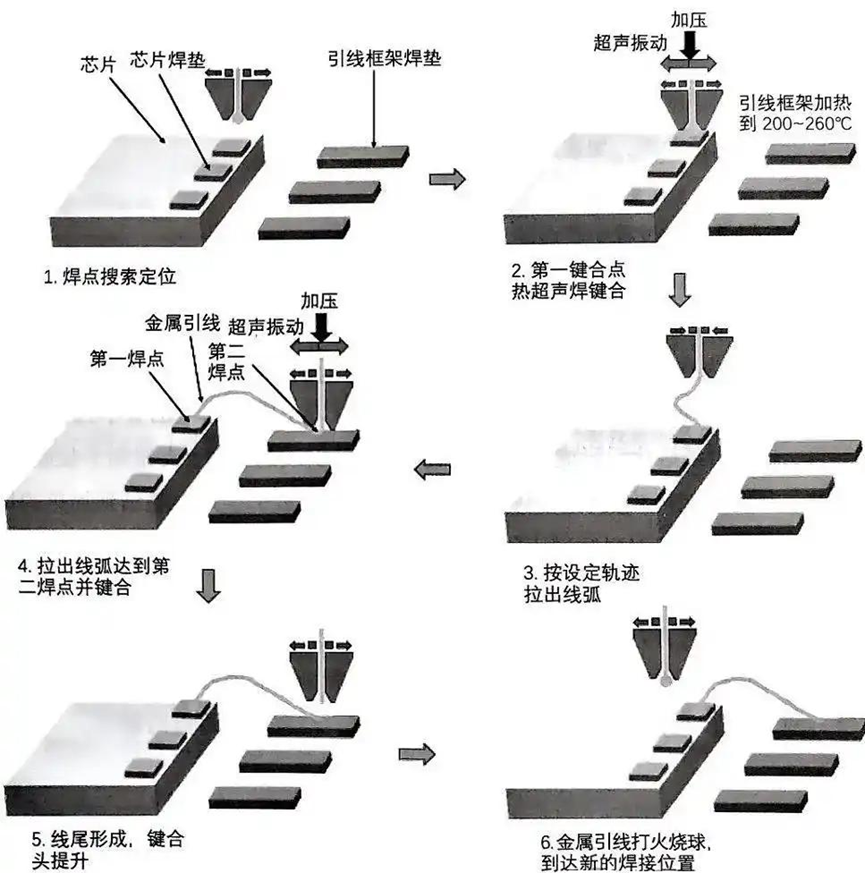

The physical mechanism of the wire

welding process is complex. Thermosonic bonding is

the most commonly used technique, through the synergistic action of temperature

(150-250°C), pressure (50-200g) and ultrasonic waves (20-60kHz), so that the

metal leads and the surface of the pad are plastically deformed, destroying the

oxide layer and forming interatomic bonds. The whole process is divided into

six steps: burning the ball (electric ignition to form a gold ball with a

diameter of 50-100μm at the top of the gold wire), first bonding (combining the

gold ball with the chip pad), pulling the wire (forming a wire arc), second

bonding (combining with the substrate pad), breaking the wire, and moving to

the next pad, the whole process takes < 100ms.

The choice of lead material has its own advantages and disadvantages. Gold wire (99.99% purity), good electrical conductivity (resistivity 1.58μΩ・cm), and chemical stability, are the first choice for high-frequency chips, but they are expensive (about 400 yuan/gram), accounting for 10-15% of the packaging cost. Copper wire (99.95% purity) costs only 1/5 of gold wire, has a resistivity of 1.67μΩ・cm, and has similar performance, but is prone to oxidation, and needs to be soldered in a nitrogen atmosphere (oxygen content <10ppm), making it suitable for low- to medium-end products. Silver wire (resistivity 1.59μΩ・cm) has excellent performance, but it is easy to migrate and is rarely used. Aluminum wire (resistivity 2.65μΩ・cm) has the lowest cost, but has low bond strength and a yield of <90%, so it is gradually being phased out.

Key indicators of wire quality include: bond strength (gold wire > 15g, copper wire > 20g), wire arc

height (±10μm), and solder joint diameter (gold wire ball weld diameter is

2.5-3 times the wire diameter). The tensile testing machine samples 5 times per

hour to ensure that the bond strength meets the standard; AOI equipment checks

the shape of the solder joints and whether there are defects such as virtual

welding. Tests of an automotive-grade MCU showed that the contact resistance of

the solder wire should be controlled at <50mΩ, otherwise it would lead to a

decrease in signal integrity.

The technological breakthrough of high-density welding wire is remarkable. As the number of chip I/O has increased from hundreds to thousands, the solder wire spacing has been reduced from 50μm to 30μm, and the 25μm pitch can be achieved with copper wire wedge soldering technology, which can accommodate 1000 solder joints per square millimeter. A 5G chip has 2,000 I/O numbers through high-density soldering wires, and the data transmission rate has been increased to 10Gbps, which is 2 times faster than traditional solutions.

5. Molding: the strong "armor"

of chips

After the wire is soldered, the chip needs

to be sealed and protected, a step called mold sealing, which is like putting

on a "body armor" for the chip. The molded material should be

resistant to temperature changes (-55°C to 125°C), humidity (85% RH) and

mechanical shock, while providing good heat dissipation and insulation

properties.

The three packaging material systems

have their own merits. Plastic packaging occupies more than 90% of the market

share, using epoxy plastic encapsulation material (EMC), composed of epoxy

resin (matrix), silicon micropowder (filler, 60-80%), curing agent, etc., low

cost (about 0.1 yuan/piece), but thermal conductivity is only 0.8-1.5W/m・K, suitable for consumer electronics.

Ceramic packaging uses Al₂O₃

or AlN ceramics, with a thermal conductivity of up to

200W/m·K, good air tightness (leakage rate <

1×10⁻⁸Pa・m³/s), but the cost is 10-20 times that of

plastic packaging, and is used in the aerospace and military industry.

Metal packaging is made of Kovar alloy or

copper, which has excellent electromagnetic shielding properties and is

suitable for RF front-ends, but is heavy and costly.

The key performance indicators of epoxy

plastic encapsulants include: glass temperature (Tg>150°C),

bending strength >100MPa, volume resistivity >10¹⁴Ω cm, and water absorption <0.2%. Product testing by an EMC vendor

showed that its material retained its tensile strength > 90% and stabilized

at 4.5±0.2 after aging at 150°C/1000 hours.

The transfer molding process is the

mainstream. EMC particles (0.5-1mm diameter) are added to the transfer molding

machine, melted at 175°C (viscosity 50-100Pa・s), then

injected into the mold at 10-30MPa pressure, completely coated with the chip

and leads, and cured at 180°C for 60-120 seconds. The mold temperature should

be controlled within ±2°C to ensure uniform material flow and avoid bubbles

(bubble rate < 0.1%, diameter < 50μm).

Post-curing process is essential. The molded product is baked at 175°C for 4-8 hours to fully cross-link EMC (cure >95%) to improve mechanical strength and moisture resistance. One test showed that post-curing increased EMC's elongation at break from 3% to 5% and improved impact resistance by 40%.

6. Subsequent process: fine processing

from rough blanks to finished products

After molding, the chip also needs to

undergo a series of fine processing to become a qualified product, and these

processes are like "dressing up" the chip to ensure that its

performance, appearance and reliability meet the standard.

The de-flash

process removes excess material from the mold seal. Soak in 10-20% nitric acid

solution (temperature 50-60°C) for 10-15 minutes to dissolve the spill, then

rinse the residue with high-pressure water (5-10MPa) to ensure a surface

roughness of Ra<1μm and no residual spillage (width <50μm). For

lead-frame packages, EMC residue on the pins also needs to be removed, which

can affect subsequent plating.

Ball placement is a critical step in BGA encapsulation. Solder paste (viscosity

100-200Pa・s) is printed on the substrate pad, then

solder balls (diameter ± 0.3-0.8mm) are placed with a ball planter (accuracy

5μm) and melted in a reflow oven (245°C±5°C) to form a solder joint. The

coplanarity of the solder balls should be controlled at <25μm, otherwise it

will lead to poor welding. A BGA packaging factory uses X-rays to inspect the

quality of solder balls to ensure that there are no voids or voids (< void

rate is 10%).

Plating improves the solderability and corrosion resistance of the pins. Traditional

processes use Sn-PB alloy plating (5-10μm thickness), but RoHS directives have

pushed for lead-free and are now commonly used with pure tin plating (99.95%

purity) and 8-15μm thickness. After electroplating, annealing should be done at

150°C for 1 hour to inhibit the growth of tin whiskers (whisker length <

10μm) and avoid the risk of short circuit.

Trim & Form removes excess of the lead frame and bends

the pins into a standard shape (L, J, or in-line). The accuracy of the punching

die needs to reach ±10 μm, ensuring that the pin spacing deviation is < 20

μm and the verticality deviation is < 1°. A QFP package has 208 pins with a

spacing of 0.5mm and a pin coplanarity of < 50μm after rib forming, which

can make PCB soldering difficult.

Final Test

is the final check before leaving the factory. The chip is tested for function,

performance, and reliability through ATE (Automated Test Equipment), including:

DC parameters (voltage, current, resistance), AC parameters (frequency, delay),

and environmental testing (high and low temperature cycles from -40°C to 85°C).

Test coverage needs to be above 95%, ensuring a defect rate of < 100ppm. For

high-end chips, system-level testing (SLT) is also required to simulate

real-world application scenarios and find potential defects.

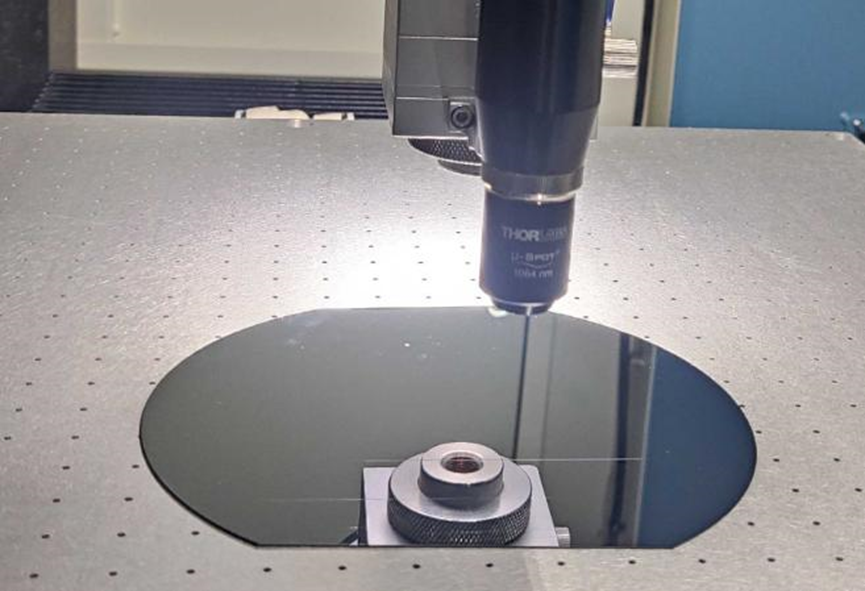

Laser marking gives the chip an "ID card". The logo, model, batch, and other

information (character height 50-100μm) is engraved on the surface of the

package with a 1064nm fiber laser, ensuring legibility and erasure resistance.

The marking speed can reach 10 characters per second, and the information of

each chip will be recorded in the MES system for full life cycle traceability.

The packaging and delivery process

ensures the safe transportation of chips. Depending on customer needs, chips

are packaged in trays, tapes & reels, or tubes, and chips with humidity

sensitivity levels (MSLs) of 1-6 need to be vacuum-packed.

Su Gongwang Security 32058302004438

Su Gongwang Security 32058302004438