Замечания:1 创始人: Site Editor Publish Time: 2026-04-23 Origin: Веб - сайт

Comprehensive Analysis of the Semiconductor

Packaging Production Line: A Precision Manufacturing Journey from Wafer to

Finished Product

In the semiconductor industry chain, the

packaging stage is akin to a "custom-tailored suit" for the chip—it must protect the fragile chip core, enable efficient electrical

performance output, and balance cost with reliability. The practices of China

Zhenhua Group Yongguang Electronics Co., Ltd. demonstrate that an advanced

semiconductor packaging production line requires the coordination of over ten

core processes, hundreds of precision equipment, and dozens of special

materials to transform a 300mm silicon wafer into a final chip product usable

in electronic devices. This article systematically dissects the complete

process flow of semiconductor back-end packaging, revealing the technical

details and quality control points of each operation, and showcasing the unique

charm of this hybrid complex manufacturing process.

I. Grinding: Precision "Sculpting" of Wafer Thinning

The grinding process (backside thinning) is

the first critical step in semiconductor packaging, serving to "pave the

way" for subsequent processes—by precisely

removing excess material from the backside of the silicon wafer, it lays the

foundation for chip dicing, heat dissipation, and miniaturization. While

seemingly simple, this process requires balancing efficiency and quality at the

micron-level precision.

The thinning process has dual technical objectives. Mechanically, the original thickness (typically 725Мm ± 25Мm for an 8-inch wafer) must be reduced to a target range of 200–500Мm, with specific values depending on the chip type: power devices typically retain 300–500Мm for enhanced heat dissipation, while RF chips can be thinned to 200Мm or even thinner for miniaturization. Test data from a certain automotive-grade IGBT module show that thinning the silicon wafer from 500Мm to 300Мm reduces device thermal resistance by 15% and increases power cycle life by 20%. From a materials perspective, the thinning process must maintain wafer integrity, control edge chipping to within 5Мm, and achieve a surface roughness Ra < 0.5Мm to avoid crack propagation during subsequent dicing.

The precision control system of grinding equipment involves triple safeguards. Modern grinders (e.g., DISCO DFG-8540) employ a three-stage process of "coarse grinding—fine grinding—polishing": the coarse grinding stage uses a 1200-grit diamond wheel to remove 70% of the target thickness at a feed rate of 5Мm/s; the fine grinding stage switches to a 3000-grit wheel to remove 25% of the thickness, reducing the feed rate to 1Мm/s; finally, chemical mechanical polishing (CMP) removes the remaining 5%, achieving a surface flatness with TTV (Total Thickness Variation) < 5Мm. An ionized water spray system operates throughout the process, cooling the grinding wheel (preventing localized overheating and stress in the wafer) and flushing away grinding debris (avoiding secondary scratches), with its flow rate precisely controlled at 500 ± 50 mL/min.

Automation integration significantly enhances efficiency. Through automated inline connection with dicing equipment (Load Port docking), unmanned wafer transfer is achieved, reducing single-wafer processing time from 3 minutes with manual operation to 90 seconds, while minimizing contamination risks from human contact (contaminants with particle size > 0.3Мm controlled to < 10 per wafer). Production data from a packaging plant show that after adopting a fully automated grinding line, equipment utilization increased from 65% to 85%, and monthly capacity rose by 30%.

II. Dicing: Precision "Cutting" of Wafer Separation

The dicing process is like "slicing a

cake," precisely dividing the entire wafer into individual dies according

to chip dimensions. Its quality directly determines the yield of subsequent die

attachment—minor dicing defects can lead to the

scrapping of chips worth hundreds of dollars. The core of dicing technology

lies in ensuring cutting precision while minimizing damage to the chip's active

areas.

Pre-dicing preparation processes are crucial. First, a film mounting operation is performed, adhering the thinned wafer face-down onto a UV tape (typically 100Мm ± 10Мm thick), with tape adhesion precisely controlled at 50–80 g/in (1 in = 25.4 mm)—insufficient adhesion can cause chip displacement during dicing, while excessive adhesion may damage the chip during subsequent pick-up. The film mounting process is conducted in a Class 100 cleanroom, ensuring a bubble rate < 0.1% and bubble diameter < 50Мm. Next, frame fixation involves mounting the wafer with the film onto a metal frame (typically 4-inch or 6-inch specifications), with frame flatness error < 0.1 mm to ensure uniform force distribution during dicing.

Parameter optimization of diamond cutting is technically key. Dicing saws (e.g., K&S 7700) use diamond blades with a thickness of 25Мm (blade diameter 50mm ± 0.1mm), with cutting speeds adjusted based on chip material properties: typically 30–50 mm/s for silicon-based chips, reduced to 10–20 mm/s for gallium arsenide chips to minimize chipping. The cutting depth must be strictly controlled within the range of "penetrating the wafer without damaging the frame," typically set to wafer thickness + 20Мm (e.g., 320Мm cutting depth for a 300Мm wafer), ensuring a cut-through rate of 90%–100%. An ionized water cooling system continuously flushes the cutting area at a flow rate of 300 mL/min, both reducing temperature (preventing thermal damage to the wafer) and clearing cutting debris (avoiding blade clogging).

Quantitative inspection standards for dicing quality are strict and clear. Key indicators include: chipping size < 5Мm (active area edge) and < 10Мm (non-active area); dicing street width deviation < 3Мm; chip dimensional accuracy ± 5Мm. Dicing quality inspection for a certain CMOS image sensor shows that when chipping size is controlled within 3Мm, the subsequent die attachment yield can reach 99.5%, whereas when chipping exceeds 8Мm, the yield drops sharply to 85%.

III. Die Attachment: Precision "Assembly" of Chip Placement

The die attachment process is a critical

step in establishing a mechanical connection between individual dies and the

lead frame, akin to "settling the chip in its home." This process

requires achieving a strong bond while ensuring high-precision placement,

creating favorable conditions for subsequent bonding processes. Modern die

attach machines have achieved sub-micron precision, meeting the demands of

high-density packaging.

The workflow of fully automated die attachment systems is highly coordinated. The system consists of a loading unit (wafer cassette identification and positioning), a vision positioning system (dual-camera calibration, accuracy ± 0.5Мm), a pick-and-place mechanism (vacuum nozzle, diameter customized based on chip size, typically 0.3–2 mm), and a lead frame transport system. During operation, the system first identifies the chip model via barcode, calling up the corresponding parameter library; then, the vision system captures the chip surface alignment marks and lead frame reference points to calculate the precise placement position; the pick-and-place mechanism picks up the chip at a speed of 50 mm/s (vacuum level -80 kPa ± 5 kPa), moves to the target position, and releases it (vacuum level switched to +20 kPa), completing the die attachment action. The entire process is completed within 1.5 seconds and is monitored in real-time by CCD cameras to ensure no missing or misplaced dies.

Bonding material selection strategies vary by application. Epoxy resin (e.g., silver paste) is the most commonly used bonding material, characterized by low cost (approximately 0.5 RMB per piece) and simple processing, suitable for mid-to-low-end products like consumer electronics. Its bond strength must be > 20 MPa, thermal conductivity > 1 W/m·K, and curing conditions are typically 150°C/60 min. Eutectic solder (e.g., Au-Si alloy) is suitable for high-frequency, high-reliability scenarios, achieving atomic-level bonding through a 370°C eutectic reaction, with bond strength > 30 MPa and thermal conductivity > 30 W/m·K, but it is more expensive (approximately 5 RMB per piece) and mostly used in aerospace applications. Glass solder is suitable for high-temperature environments (> 300°C), achieving bonding through the melting and recrystallization of glass powder, with insulation resistance > 10¹² Ω, widely used in automotive engine control modules.

Standardization and special treatment of lead frames balance efficiency and flexibility. Standard lead frames (e.g., TO-220, SOP-8) are made of copper alloy (C19400), with a thickness of 0.25–0.5 mm, and surface-plated with nickel (thickness 3–5 Мm) for oxidation resistance, supplied in bulk by specialized manufacturers with a delivery lead time < 7 days. For new chip models, custom lead frames are required, necessitating mold design (cycle approximately 2 weeks), material selection, and process validation, with an overall development cycle of about 4 weeks, three times longer than for standard products. Experience from a certain RF chip manufacturer shows that using standardized lead frames can stabilize die attachment yield above 99%, whereas initial yield for custom frames typically requires 2–3 weeks of debugging to reach 95%.

IV. Bonding: Microscopic "Bridges" for Electrical Connections

The bonding process establishes electrical

connections between the chip pads and the lead frame through metal wires, akin

to "laying wires" for the chip. Conducted at the micron scale, this

process requires precise control of temperature, pressure, and ultrasonic

energy to form reliable metallurgical bonds. Bonding quality directly

determines the chip's electrical performance and long-term reliability, making

it one of the most technologically intensive processes in the packaging

production line.

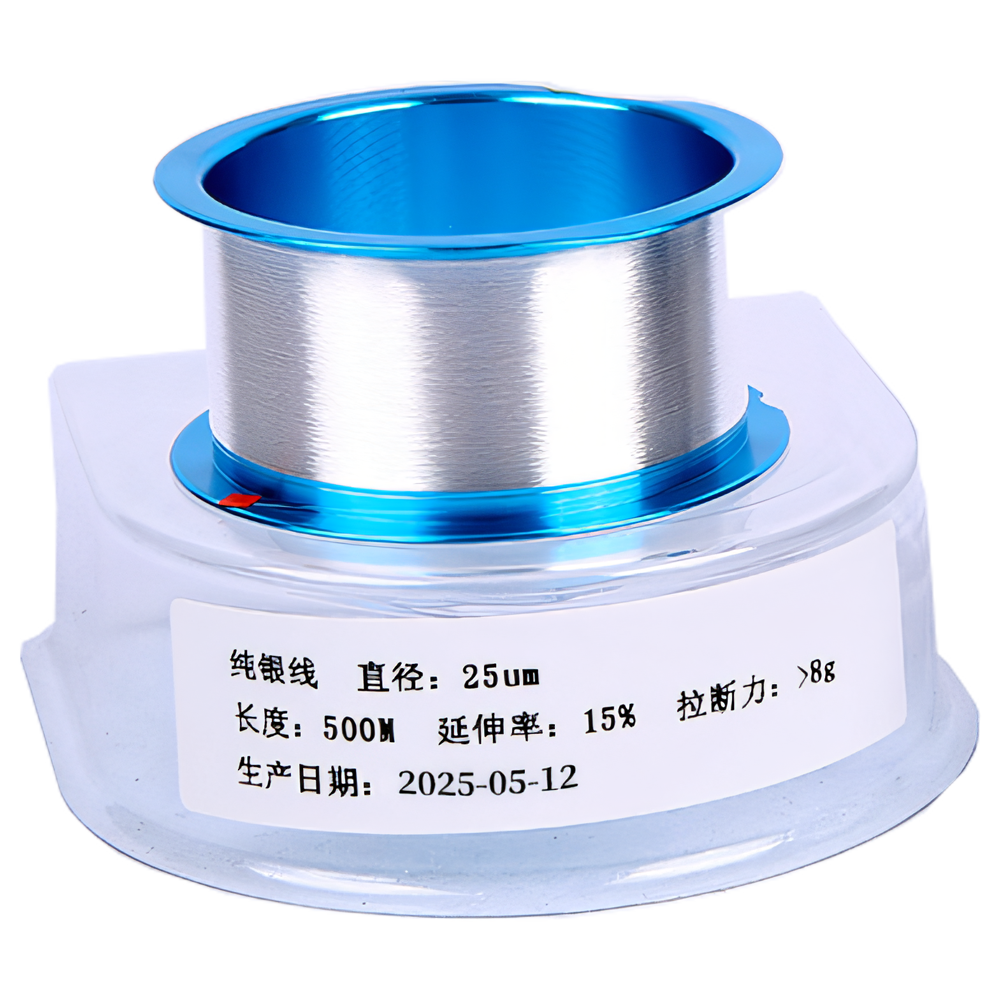

The characteristics and selection of bonding materials affect connection quality. Gold wire (purity 99.99%) offers excellent conductivity (resistivity 1.587×10⁻⁸ Ω·m) and oxidation resistance, making it the preferred choice for high-frequency, high-reliability products. However, its high cost (approximately 400 RMB per gram) limits its use primarily to high-end chips like RF front-ends. Copper wire (purity 99.95%) costs only 1/5 of gold wire and has similar conductivity (resistivity 1.67×10⁻⁸ Ω·m), but it is prone to oxidation and requires bonding under nitrogen protection (oxygen content < 10 ppm), making it suitable for cost-sensitive products like power devices. Bonding wire diameter is typically 25Мm (corresponding to pad pitch of 70Мm), with fine-pitch chips using 18Мm diameter wire, and power devices using 50–100Мm thick wire.

The technical characteristics of the three mainstream bonding processes each have their focus. Thermosonic ball bonding is the most widely used technology, where under the synergistic action of 150–250°C temperature, 0.5–1.5 N pressure, and 20–60 kHz ultrasound, a gold ball (diameter 2.5–3 times the wire diameter) forms at the wire tip, creating a strong bond with the pad. Bond strength > 15g (for 25Мm wire diameter) makes it suitable for most digital and analog chips. Ultrasonic bonding requires no heating, achieving connections between aluminum wire and aluminum pads through high-frequency vibration, suitable for temperature-sensitive devices (e.g., MEMS sensors), but bond strength is slightly lower (> 10g). Thermocompression bonding relies on high temperature (300–400°C) and high pressure (1–2 N) to form connections, suitable for power bonding with thick aluminum wires (> 50Мm), with the highest bond strength (> 30g), but a larger heat-affected zone.

Multi-dimensional control of bonding quality ensures reliability. The vision inspection system checks bond shape (ball bond roundness > 0.8, wedge bond aspect ratio 1.5–2.5), absence of cracks and voids; pull testing (sampled 5 times per hour) ensures strength meets standards; ultrasonic imaging detects internal bonding conditions (bonded area > 70%). Quality control data for a certain automotive-grade MCU show that when the standard deviation of bond strength is controlled within 3g, the contact resistance increase after 150°C/1000 hours aging is < 10%, far better than the industry standard of 20%. Since the number of pins to be bonded per chip ranges from 2 to 300, the bonding process typically requires the most equipment (8–12 bonders per production line) and requires operator real-time monitoring (bonding parameters and images displayed on LCD screens).

V. Molding: The Sturdy "Armor" for Chip Protection

The molding process encapsulates the chip

and bonded wires with epoxy resin, providing mechanical protection, moisture

and contamination resistance, and heat dissipation pathways, akin to putting a

"bulletproof vest" on the chip. This process requires completing

resin flow, filling, and curing under high temperature and pressure, demanding

extremely high requirements for mold design and process parameter control.

The dominance of molding materials and processes is clear. Over 95% of global chips use epoxy molding compound (EMC) for packaging. This material consists of epoxy resin (matrix), silica filler (60–80% by weight), curing agent, and release agent, offering good insulation (volume resistivity > 10¹⁴ Ω·cm), high mechanical strength (flexural strength > 100 MPa), good temperature resistance (Tg > 150°C), and low cost (approximately 0.1 RMB per unit). In contrast, ceramic packaging (about 4% share), while offering superior performance (thermal conductivity > 20 W/m·K, temperature resistance > 300°C), costs 10–20 times more than molding and is used only in high-end military and aerospace products.

Precise control of the transfer molding process determines packaging quality. The process consists of four steps: preheating (heating the lead frame and chip to 100–150°C to reduce resin flow resistance); mold closing (mold closes with 5–10 MPa pressure to ensure sealing); resin injection (injecting molten EMC into the mold cavity at 10–30 MPa pressure, filling speed 5–10 cm/s, ensuring no bubbles); curing (maintaining at 175°C ± 5°C for 60–120 seconds for complete resin cross-linking). Key parameters include: fill time (< 10 seconds to prevent premature resin curing during filling); degree of cure (> 95%, detected by DSC); and mold cavity pressure uniformity (deviation < 5%). Optimization of a QFP packaging molding process showed that increasing injection pressure from 15 MPa to 20 MPa reduced void rate from 3% to 0.5%, but excessive pressure (> 25 MPa) could cause wire deformation.

Customization and cost balance of molds require consideration. Molding molds are customized based on package size and pin count, with mold costs ranging from tens of thousands to hundreds of thousands of RMB, and a lifespan of about 1 million cycles. For mass-produced products, mold costs can be amortized per chip (approximately 0.001–0.01 RMB per unit), having a minor impact; however, for small-batch trial production, mold costs may account for over 30% of the total packaging cost. By adopting quick-change mold technology (mold change time < 30 minutes), mold utilization can be improved. A certain R&D-oriented packaging plant's practice showed that this technology reduced multi-variety small-batch production costs by 20%.

VI. Deflashing: Fine "Trimming" of Package Formation

The deflashing (trimming and forming)

process is like "pruning branches and leaves," removing excess

material (gates, flashes, etc.) remaining after molding and punching the lead

frame into individual chip units, preparing for subsequent plating and pin

forming. This process requires precise control of punching force and position

to avoid damage to the package body and leads.

The punching process has dual technical objectives. First, removing flashes, completely eliminating overflow material (typically thickness < 50Мm) and gate residue (length < 1 mm) generated during molding, ensuring a smooth package appearance without burrs (height < 5Мm). Second, unit separation, punching the interconnected multiple chips into individual units according to design dimensions, requiring a cutting accuracy of ± 0.1 mm to ensure no adhesion between adjacent chips. Punching equipment (e.g., Schmid punch press) uses carbide dies (hardness HRC 60–65), punching speed 100–300 strokes/minute, with punching force adjusted based on package size (typically 5–20 kN).

Key quality inspection indicators include: package body corner chipping (depth < 0.2 mm); cracks (not allowed); lead deformation (offset < 0.1 mm); and residual flash (width < 0.1 mm). Deflashing quality inspection for a certain BGA package showed that when mold wear exceeded 0.01 mm, the residual flash rate increased from 0.1% to 2%, necessitating timely mold replacement (typically replaced every 1 million chips produced).

VII. Plating, Bending, and Laser Marking: The Chip's "Identity" and Performance Enhancement

These three consecutive processes treat the

chip from three dimensions: electrical performance, mechanical adaptation, and

information identification. They are the final preparation stages before the

chip enters the testing phase, with each step affecting the final chip quality

and traceability.

The protective and connection functions of the plating process are important. Through electrodeposition, a metal coating (typically tin or tin-lead alloy, thickness 5–15Мm) is formed on the surface of the lead pins. Its purposes are: first, oxidation prevention (the tin layer protects the copper leads from oxidation before storage and soldering); second, improved solderability (tin's low melting point facilitates subsequent PCB soldering). The plating process is conducted in an acidic bath (pH 1–3), with current density 1–3 A/dm² and temperature 25–35°C, ensuring uniform coating (thickness deviation < 10%), no pinholes (< 1 per square centimeter), and good adhesion (no peeling in tape test). For lead-free products, pure tin coating (tin content > 99.5%) must be used, and its whisker growth (length < 10Мm) must be controlled to meet RoHS environmental requirements.

The precise shaping of bending (pin forming) determines assembly compatibility. Based on PCB assembly requirements, pins are bent into specific shapes: L-type (surface mount, pin length 1–2 mm, bend angle 90° ± 1°); J-type (surface mount, offering better mechanical strength, bend radius 0.3–0.5 mm); and through-hole type (for mounting through the PCB, pin length 5–10 mm, perpendicularity deviation < 1°).

Безопасность сети 32058300438

Безопасность сети 32058300438